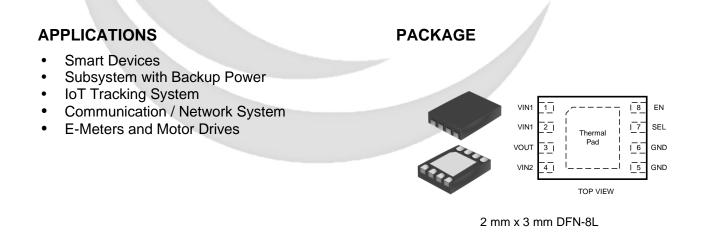

GLF4003 Ultra-low IQ, Asymmetrical Power Mux IC with Priority, Auto & Manual Input Selection Product Specification

#### DESCRIPTION

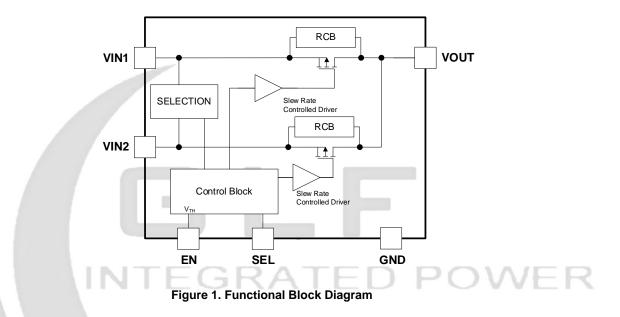

The GLF4003 is an integrated power multiplexer IC with dual independent power switches connected to a single output pin to enable seamless transition between two input sources. The GLF4003 features asymmetrical power FET characteristics. Channel 1 (VIN1) provides lower conduction resistance to support 2.0 A continuous current capability. The current rating of another channel (VIN2) is 1.5 A. It is an ideal solution for a power system with an internal back up power source.

The GLF4003 provides an automatic selection, a manual selection and VIN1 priority selection mode. The switching of these three modes is executed by combining the EN and SEL pin settings. The EN input pin has an internal threshold voltage to offer a preference to select the channel 1 (VIN1) power source. In the automatic input selection mode, the GLF4003 automatically selects a higher input voltage source between two input power sources.

The GLF4003 prevents cross conduction current between two input sources. When VOUT is higher than VIN, the GLF4003 prevents the reverse current from the output to the input, no matter which input supply is applied.

#### FEATURES

- Two-Input and Single-Output Power Multiplexer IC

- Auto and Manual Input Selection Mode

- VIN1 Priority Selection Mode

- Wide Input Range: 1.5 V to 4.8 V

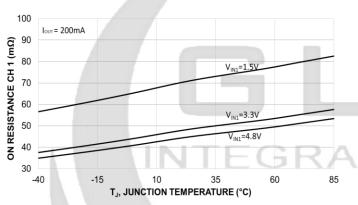

- Low R<sub>ON</sub>

- $\circ~$  Channel 1, VIN1 = 45 m $\Omega$  Typ at 4.8 V\_{IN1}

- $\circ~$  Channel 2, VIN2 = 77 m $\Omega$  Typ at 4.8 V\_{IN2}

- IOUT Max

- Channel 1 = 2.0 A

- Channel 2 = 1.5 A

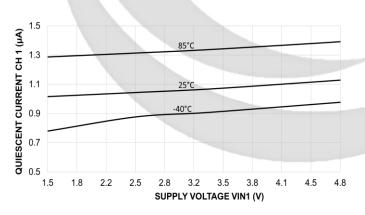

- Ultra-Low Supply Current at Operation

- o  $I_Q$ : 1.1 µA Typ at 4.8 V<sub>IN</sub>

- Ultra-Low Stand-by Current

- $\circ$  ~ I\_{SD} : 400 nA Typ at 4.8  $V_{\text{IN}}$

- Reverse Current Blocking Protection

- Operating Temperature Range:

- -40 °C to 85 °C

#### PRODUCT INFORMATION

|              | -           | Channel            | 1 (VIN1)         | Channel                                    | 2 (VIN2)         |            |  |

|--------------|-------------|--------------------|------------------|--------------------------------------------|------------------|------------|--|

| Part Number  | Top<br>Mark | Ron1<br>at 4.8 Vin | Ι <sub>Ουτ</sub> | R <sub>0N2</sub><br>at 4.8 V <sub>IN</sub> | Ι <sub>Ουτ</sub> | Package    |  |

| GLF4003-D3G7 | HG          | 45 mΩ              | 2.0 A            | <b>77</b> mΩ                               | 1.5 A            | DFN 2x3-8L |  |

#### FUNCTIONAL BLOCK DIAGRAM

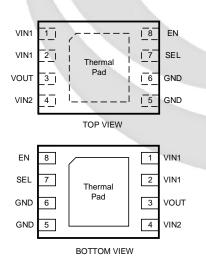

#### **PIN CONFIGURATION**

#### **PIN DEFINITION**

| Pin # | Name    | Description                                                                                         |

|-------|---------|-----------------------------------------------------------------------------------------------------|

| 1, 2  | VIN1    | IC Input 1                                                                                          |

| 3     | VOUT    | IC Output                                                                                           |

| 4     | VIN2    | IC Input 2                                                                                          |

| 5, 6  | GND     | Ground                                                                                              |

| 7, 8  | SEL, EN | Logic control, SEL and EN high and low combinations determine the selection mode. Refer to table 1. |

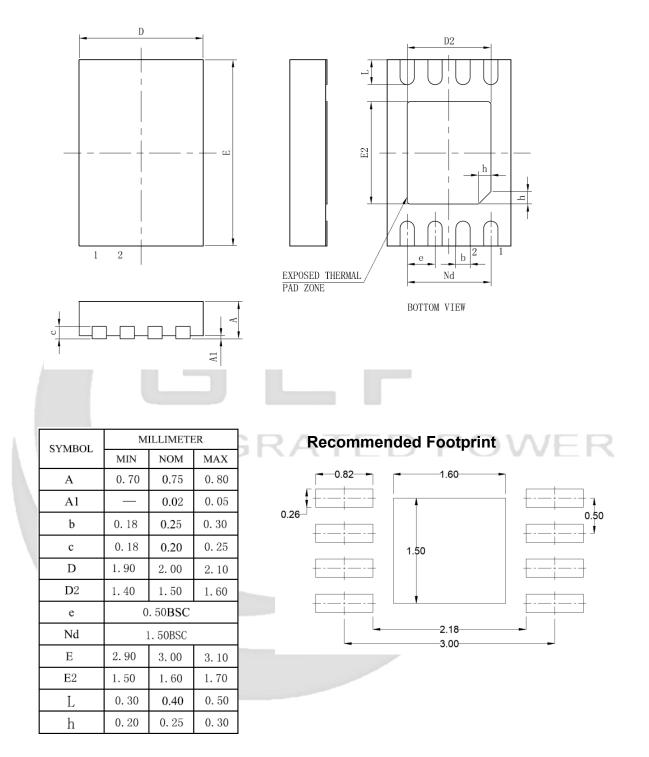

Figure 2. 2 mm x 3mm DFN-8L

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions; extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           |                                         | Min.                              | Max. | Unit |      |

|------------------|-----------------------------------------|-----------------------------------|------|------|------|

| Vin1, Vin2, Vout | Each Pin Voltage Range to               | GND                               | -0.3 | 6    | V    |

| Ven, Vsel        | Control Pin Voltage                     |                                   | -0.3 | 6    | V    |

| laum.            | Continuous Current through              | Continuous Current through VIN1   |      |      |      |

| Ιουτ             | Continuous Current through              |                                   | 1.5  | А    |      |

| TJ               | Maximum Junction Tempera                |                                   | 125  | °C   |      |

| T <sub>STG</sub> | Storage Junction Temperate              | -65                               | 150  | °C   |      |

| T <sub>A</sub>   | Ambient Operating Temperature Range     |                                   |      | 85   | °C   |

| θја              | Thermal Resistance, Junction to Ambient |                                   |      | 110  | °C/W |

|                  | Electrostatic Discharge                 | Human Body Model, JESD22-A114     | ±2   |      | L\ / |

| ESD              | Capability                              | Charged Device Model, JESD22-C101 | ±2   |      | kV   |

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                              | Parameter           | Min. | Max. | Unit |

|-------------------------------------|---------------------|------|------|------|

| V <sub>IN1</sub> , V <sub>IN2</sub> | Input Voltage       | 1.5  | 4.8  | V    |

| V <sub>EN</sub> , V <sub>SEL</sub>  | Control Pin Voltage | 0    | 4.8  | V    |

INTEGRATED POW

## ELECTRICAL CHARACTERISTICS

$V_{IN1} = V_{IN2} = 1.5$  V to 4.8 V and  $T_A = 25$  °C. Unless otherwise noted

| Symbol                                                           | Parameter                                                                   | Conditions                                                                              |                        |     | Тур | Max | Units |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------|-----|-----|-----|-------|--|--|

| Basic Operation                                                  |                                                                             |                                                                                         |                        |     |     |     |       |  |  |

| I <sub>STBY_VIN1,2</sub> VIN Unselect Channel<br>Standby Current |                                                                             | V <sub>IN1</sub> = 4.8 V, I <sub>OUT</sub> = 0 mA<br>SEL=VIN1, EN= 0 V, VOUT=VIN2<br>or | T <sub>A</sub> = 25 °C |     | 0.9 | 1.1 |       |  |  |

|                                                                  | $V_{IN2} = 4.8 \text{ V}, I_{OUT} = 0 \text{ mA}$<br>EN=SEL=VIN2, VOUT=VIN1 | T <sub>A</sub> = 85 °C                                                                  |                        | 1.2 |     |     |       |  |  |

| _                                                                |                                                                             | $V_{IN1} = 4.8 \text{ V}, I_{OUT} = 0 \text{ mA}$<br>EN=SEL=VIN1, VOUT=VIN1             | T <sub>A</sub> = 25 °C |     | 1.1 | 1.6 | μA    |  |  |

| I <sub>Q_VIN1,2</sub> VIN Quiescen                               | VIN Quiescent Current                                                       | or<br>V <sub>IN2</sub> = 4.8 V, I <sub>OUT</sub> = 0 mA<br>EN=VIN1, SEL= 0 V, VOUT=VIN2 | T <sub>A</sub> = 85 °C |     | 1.5 |     |       |  |  |

|                                                                  | VIN Shutdown Current                                                        | V <sub>IN1,2</sub> = 4.8 V, V <sub>SEL</sub> = 0 V, V <sub>EN</sub> = 4.8 V             | $T_A = 25$ °C          |     | 0.4 | 0.7 |       |  |  |

| SD_VIN1,2                                                        | VIN Shutdown Current                                                        | Vout = High-Z                                                                           | T <sub>A</sub> = 85 °C |     | 0.9 |     | μA    |  |  |

| I <sub>EN</sub> , I <sub>SEL</sub>                               | EN and SEL Pin Leakage                                                      | $V_{EN} = V_{SEL} = 4.8 V$                                                              |                        |     | 4   |     | nA    |  |  |

# **GLF4003**

# Ultra-low I<sub>Q</sub>, Asymmetrical Power Mux IC with Priority, Auto & Manual Input Selection

| Symbol           | Parameter                                   |                                                     | Conditions                               |                        | Min    | Тур  | Max | Units |

|------------------|---------------------------------------------|-----------------------------------------------------|------------------------------------------|------------------------|--------|------|-----|-------|

|                  |                                             |                                                     | 000 1                                    | $T_A = 25$ °C          |        | 45   | 52  |       |

|                  |                                             | $V_{IN1} = 4.8 V, I_{O}$                            | T <sub>A</sub> = 85 °C                   |                        | 54     |      |     |       |

|                  |                                             |                                                     | 000 4                                    | T <sub>A</sub> = 25 °C |        | 49   | 56  |       |

|                  | Channel 1                                   | $V_{IN1} = 3.3 V, I_0$                              | <sub>UT</sub> = 200 mA                   | T <sub>A</sub> = 85 °C |        | 58   |     |       |

|                  | On-Resistance                               |                                                     |                                          | T <sub>A</sub> = 25 °C |        | 62   | 70  |       |

|                  |                                             | V <sub>IN1</sub> = 1.8 V, Io                        | <sub>UT</sub> = 200 mA                   | T <sub>A</sub> = 85 °C |        | 75   |     |       |

|                  |                                             |                                                     |                                          | T <sub>A</sub> = 25 °C |        | 71   | 79  |       |

| _                |                                             | $V_{IN1} = 1.5 V, I_0$                              | <sub>UT</sub> = 200 mA                   | T <sub>A</sub> = 85 °C |        | 83   |     |       |

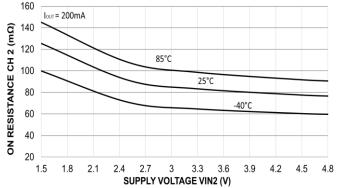

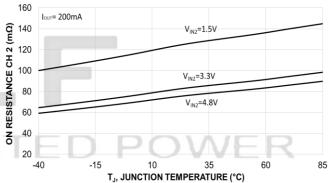

| R <sub>ON</sub>  |                                             |                                                     |                                          | $T_A = 25$ °C          |        | 77   | 84  | mΩ    |

|                  |                                             | V <sub>IN2</sub> = 4.8 V, Io                        | ut = 200 mA                              | T <sub>A</sub> = 85 °C |        | 91   |     |       |

|                  |                                             |                                                     |                                          | T <sub>A</sub> = 25 °C |        | 84   | 90  |       |

|                  | Channel 2                                   | $V_{IN2} = 3.3 V, I_0$                              | <sub>UT</sub> = 200 mA                   | T <sub>A</sub> = 85 °C |        | 99   |     |       |

|                  | On-Resistance                               |                                                     |                                          | T <sub>A</sub> = 25 °C |        | 109  | 115 |       |

|                  |                                             | $V_{IN2} = 1.8 V, I_O$                              | <sub>UT</sub> = 200 mA                   | T <sub>A</sub> = 85 °C |        | 132  |     |       |

|                  |                                             | V <sub>IN2</sub> = 1.5 V, I <sub>OUT</sub> = 200 mA |                                          | T <sub>A</sub> = 25 °C |        | 125  | 132 | -     |

|                  |                                             |                                                     |                                          | T <sub>A</sub> = 85 °C |        | 145  |     |       |

|                  |                                             | VIN1 or VIN2 = 1                                    | .5 V to 4.8 V                            |                        |        | 1.0  | 1.1 | V     |

| $V_{TH}$         | EN Pin Threshold Voltage                    | Hysteresis                                          |                                          |                        |        | 50   |     | mV    |

| V <sub>IH</sub>  | SEL Input Logic High Voltage                | $V_{IN1}$ or $V_{IN2} = 1.5$ V to 4.8 V             |                                          |                        | 1.2    |      |     |       |

| V <sub>IL</sub>  | SEL Input Logic Low Voltage                 | $V_{IN1}$ or $V_{IN2} = 1.5$ V to 4.8 V             |                                          |                        |        |      | 0.3 | V     |

|                  | Current Blocking Protection                 |                                                     |                                          |                        |        |      |     |       |

| t <sub>RCB</sub> | RCB Response Time (1)                       | Vout > Selecte                                      | d V <sub>IN</sub> + 1 V                  |                        |        | 2    |     | μs    |

| VRCB_TH          | RCB Protection Threshold                    | Vout – Vin                                          | ATE                                      | D P                    | $\cap$ | 110  |     | mV    |

| VRCB_RL          | RCB Protection Release                      | Vin – Vout                                          |                                          |                        |        | 45   |     | mV    |

| IRCB             | RCB activation current <sup>(1)</sup>       |                                                     |                                          |                        |        | 1.44 |     | Α     |

| _                | g Characteristics                           |                                                     |                                          |                        |        |      |     |       |

| V <sub>TR</sub>  | Auto Input Selection Trigger <sup>(1)</sup> | V <sub>INX</sub> - V <sub>INY</sub> , In            | automatic select                         | ion mode               |        | 120  |     | mV    |

|                  | Switching Over time                         | V <sub>IN1</sub> to V <sub>IN2</sub>                | V <sub>IN1</sub> = 4.2 V, V <sub>I</sub> |                        | 1      | 35   |     |       |

| t <sub>SW</sub>  | In Manual Mode <sup>(1)</sup>               | V <sub>IN2</sub> to V <sub>IN1</sub>                | $C_{OUT} = 10 \ \mu F,$                  |                        |        | 17   |     |       |

|                  |                                             | V <sub>IN1</sub> = 4.2 V                            |                                          |                        | 1      | 1123 |     |       |

|                  | Turn-On Delay time                          | V <sub>IN1</sub> = 3.3 V                            |                                          |                        |        | 1107 |     |       |

|                  | Channel 1                                   | V <sub>IN1</sub> = 1.8 V                            |                                          |                        |        | 1102 |     |       |

| <b>t</b> dON     |                                             | $V_{IN2} = 4.2 V$                                   |                                          |                        |        | 718  |     |       |

|                  | Turn-On Delay time                          | $V_{IN2} = 3.3 V$                                   |                                          |                        |        | 712  |     | -     |

|                  | Channel 2                                   | $V_{IN2} = 1.8 V$                                   | Соит = 10 µF                             |                        |        | 711  |     | μs    |

|                  |                                             | $V_{IN2} = 4.2 V$                                   | $R_{L} = 100 \ \Omega$                   |                        |        | 1480 |     |       |

|                  | VOUT Rise Time                              | $V_{IN1} = 3.3 V$                                   |                                          |                        |        | 1226 |     |       |

|                  | Channel 1                                   | $V_{IN1} = 0.8 V$<br>$V_{IN1} = 1.8 V$              |                                          |                        |        | 828  |     |       |

| t <sub>R</sub>   |                                             | $V_{IN1} = 1.0$ V<br>$V_{IN2} = 4.2$ V              |                                          |                        |        | 872  |     |       |

|                  |                                             | V IINZ - 7.2 V                                      |                                          |                        |        |      |     |       |

|                  | VOUT Rise Time<br>Channel 2                 | $V_{IN2} = 3.3 V$                                   |                                          |                        |        | 729  |     |       |

**Notes:** 1. By design; characterized, not production tested.

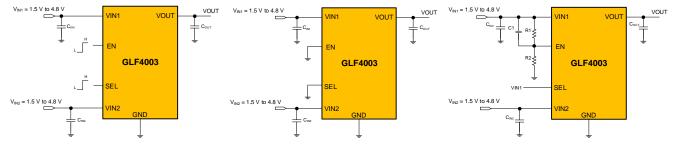

#### **APPLICATION DIAGRAM**

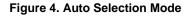

Figure 3. Manual Selection Mode

#### Mode SEL EN VOUT Function High $> V_{TH}$ VIN1 VIN1 is selected VIN2 < Vтн VIN2 is selected High Manual > Vтн Low High-Z Both channels are off Higher voltage Auto Low < Vтн Auto-Input selection between VIN1 and VIN2 > VTH by resistor VIN1 VIN1 is selected Connect to divider from VIN1 **VIN1** Priority VIN1 < V<sub>TH</sub> by resistor VIN2 VIN2 is selected divider from VIN1

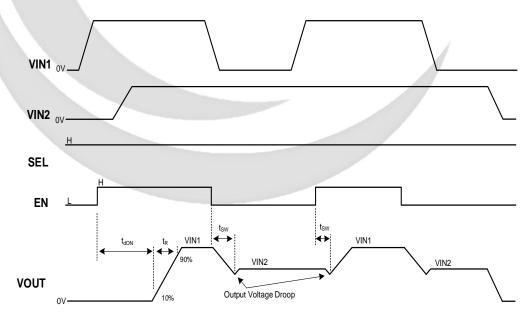

### TRUTH TABLE AND TIMING DIAGRAM

Note) VINX or VINY ≥ 1.5 V, High = VSEL > VIH, LOW = VSEL < VIL

#### Table 1. Truth Table of Input Source Selection

Note) High =  $V_{SEL} > V_{IH}$ ,  $V_{EN} > V_{TH}$ ; Low =  $V_{SEL} < V_{IL}$ ,  $V_{EN} < V_{TH}$

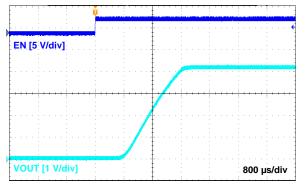

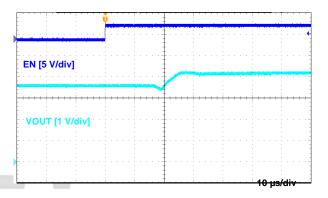

#### Figure 6. Timing Diagram, Manual Mode (Figure 3) with EN controlled by GPIO

Note) High =  $V_{SEL} > V_{IH}$ ,  $V_{EN} > V_{TH}$ ; Low =  $V_{SEL} < V_{IL}$ ,  $V_{EN} < V_{TH}$

Figure 7. Timing Diagram, VIN1 Priority Selection Mode (Figure 5) with SEL tied to VIN1

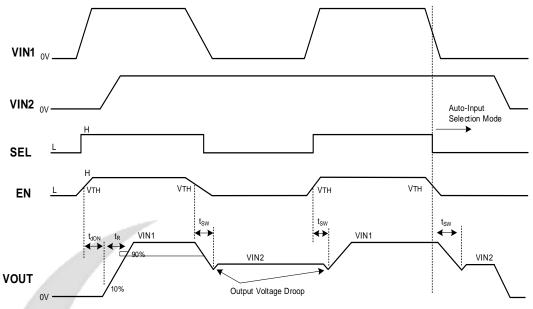

#### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8. On-Resistance vs. Supply Voltage, Channel 1

Figure 10. On-Resistance vs. Temperature, Channel 1

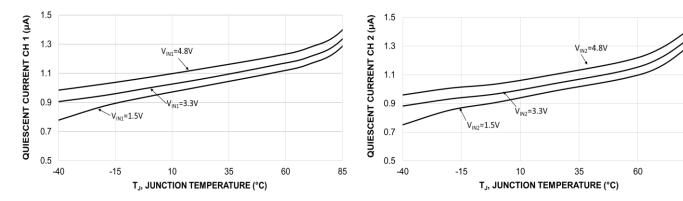

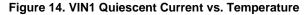

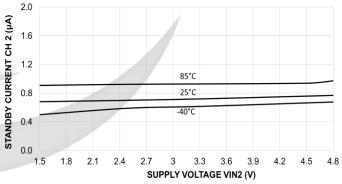

Figure 12. VIN1 Quiescent Current vs. Supply Voltage

Figure 9. On-Resistance vs. Supply Voltage, Channel 2

Figure 11. On-Resistance vs. Temperature, Channel 2

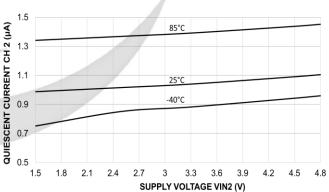

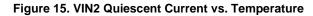

Figure 13. VIN2 Quiescent Current vs. Supply Voltage

85

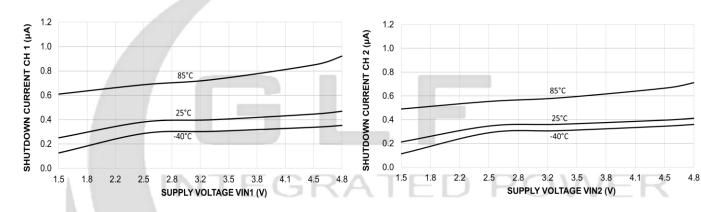

Figure 16. VIN1 Shutdown Current vs. Supply Voltage

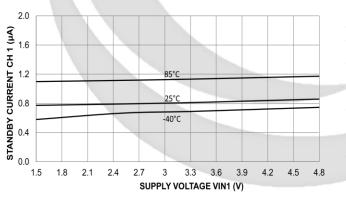

Figure 18. VIN1 Standby Current vs. Supply Voltage

Figure 17. VIN2 Shutdown Current vs. Supply Voltage

Figure 19. VIN2 Standby Current vs. Supply Voltage

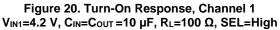

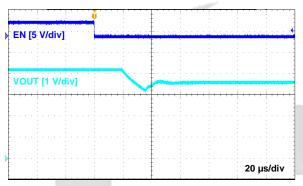

Figure 22. VOUT Switchover from 4.2 V to 3.6 V V<sub>IN1</sub>=4.2 V, V<sub>IN2</sub>=3.6 V, C<sub>IN</sub>=C<sub>OUT</sub>=10  $\mu$ F, R<sub>L</sub>=10  $\Omega$ SEL = VIN1, EN controlled by GPIO

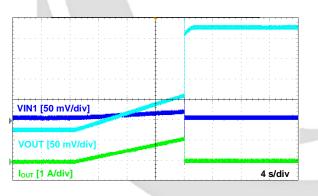

Figure 21. Turn-Off Response, Channel 1  $V_{\text{IN1}}{=}4.2$  V,  $C_{\text{IN}}{=}C_{\text{OUT}}{=}10$   $\mu F,$   $R_{\text{L}}{=}100$   $\Omega,$  SEL=High

Figure 23. VOUT Switchover from 3.6 V to 4.2 V V<sub>IN1</sub>=4.2 V, V<sub>IN2</sub>=3.6 V, C<sub>IN</sub>=C<sub>OUT</sub>=10 μF, R<sub>L</sub>=10 Ω SEL = VIN1, EN controlled by GPIO

#### APPLICATION INFORMATION

The GLF4003 is a fully integrated power mux IC with the input voltage range from 1.5 V to 4.8 V. It has asymmetrical two channels and a fixed slew rate control to limit the inrush current during turn on. It also has very low on-resistance to reduce conduction loss. In the off state, it consumes very low leakage current to avoid unwanted standby current and save input power supply.

#### Input Source Selection

According to the state of SEL and EN pins, the GLF4003 offers an automatic selection, a manual selection and VIN1 priority selection mode. In each mode, the VOUT connects to one input source. Do not leave both SEL and EN pins floating.

| Mode   | SEL  | EN                | VOUT                                 |

|--------|------|-------------------|--------------------------------------|

|        | High | > Vтн             | VIN1                                 |

| Manual | High | < Vth             | VIN2                                 |

|        | Low  | > V <sub>TH</sub> | High-Z                               |

| Auto   | Low  | < Vth             | Higher voltage between VIN1 and VIN2 |

| Table 2. | Manual and | Automatic | Selection Mode |

|----------|------------|-----------|----------------|

|          |            |           |                |

For applications, where a General-Purpose Input/Output (GPIO) pin is used to select the input source (refer to Figure 3), the GPIO pin connects directly to the EN pin, and the SEL pin is set high. When the GPIO pin is high, VIN1 is selected as the input. Conversely, when the GPIO pin is low, VIN2 is selected.

For applications, If both EN & SEL are low (refer to Figure 4), the GLF4003 will choose a higher input voltage source to VOUT automatically.

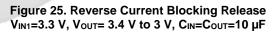

In VIN1 priority selection mode (refer to Figure 5 and Table 3), the SEL pin is connected to VIN 1 node and the EN pin is connected to the midpoint of a voltage divider formed by two resistors. The VIN1 priority selection mode operates without GPIO control. The C1 is used to stabilize the EN pin state at around  $V_{TH.}$  1 µF capacitor is recommended for the C1. When VIN1 is applied and the EN pin voltage is higher than the threshold voltage ( $V_{TH}$ ), the VOUT is powered by VIN1. As the VIN1 voltage drops, if the voltage at the EN pin falls below  $V_{TH}$ , VOUT automatically switches over to the backup channel VIN2.

| Mode     | VIN1    | VIN2    | SEL     | EN                                              | VOUT |

|----------|---------|---------|---------|-------------------------------------------------|------|

| VIN1     | ≥ 1.5 V | Х       | Connect | > V <sub>TH</sub> by resistor divider from VIN1 | VIN1 |

| Priority | ≥ 1.5 V | ≥ 1.5 V | to VIN1 | < VTH by resistor divider from VIN1             | VIN2 |

#### Table 3. VIN1 Priority Selection

#### Design Example for Switching-Over Trigger Voltage Calculation:

#### Figure 26. Design Example for V<sub>SW\_TRG</sub> Calculation

The value of the switching-over trigger voltage is determined by the following equation.

$V_{SW_{TRG}} = V_{TH} x (1 + R1 / R2)$

Where, V<sub>SW\_TRG</sub>: Switching-over trigger voltage when VIN1 is unplugged

VTH: EN pin threshold voltage

# GLF4003 Ultra-low IQ, Asymmetrical Power Mux IC with Priority, Auto & Manual Input Selection

For downstream systems requiring power supply switching with minimal output voltage drop, the GL4003 can reduces the voltage drop during transition from the primary input (VIN1) to the secondary input (VIN2) upon removal of VIN1. In this example, the switching trigger voltage is set to 3.5 V (when 4.5 V is removed) using resistors R1 (100 k $\Omega$ ) and R2 (40 k $\Omega$ ).

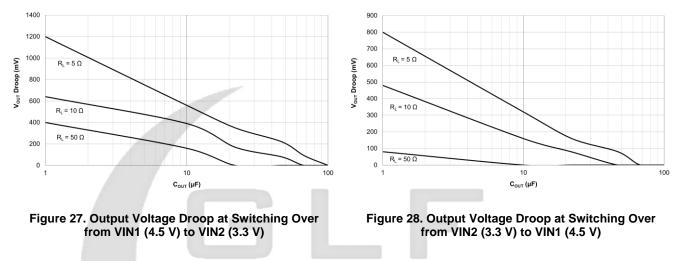

#### **Output Voltage Drop at Switching Over**

During the switching event, the output voltage drop is influenced by both the load resistance and the output capacitance. A lower load resistance at the switching point will result in a larger voltage drop. To mitigate this drop when a significant load current is needed during the transition, a sufficiently large bulk output capacitor is recommended.

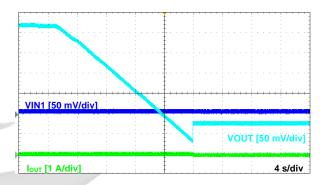

#### **Reverse Current Blocking**

The reverse current blocking protection will be enabled when either of the input voltage (VIN1 or VIN2) exceeds its minimum rating. The reverse current blocking protection triggers when the output voltage rises above an input voltage plus the reverse current blocking threshold ( $V_{RCB_TH}$ ). The main FET immediately shuts off to prevent reverse current flow. It's important to note that some reverse current might exist before  $V_{RCB_TH}$  is reached. Normal operation resumes when the output voltage falls below the input minus the reverse current blocking release voltage ( $V_{RCB_RL}$ ). An additional clamping component and a high output capacitance are recommended to safeguard against potential damage from high output voltage spikes.

#### **Board Layout**

All the external components should be placed to GLF4003 as close as possible. All traces should be as short as possible to minimize parasitic inductance. Wide traces of VIN, VOUT and GND can reduce parasitic effects under dynamic operations to improve thermal performance at high current loading.

#### PACKAGE OUTLINE

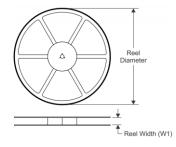

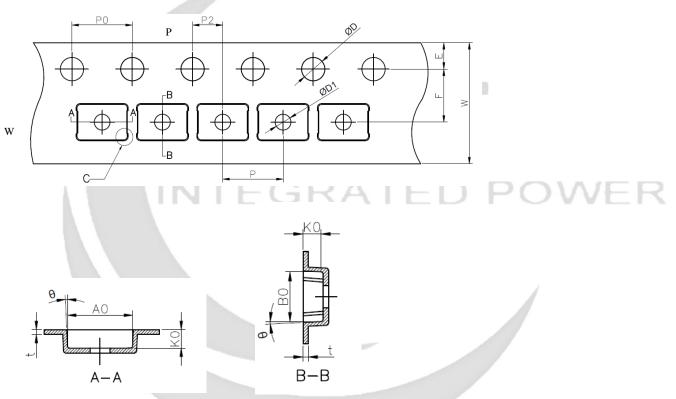

#### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

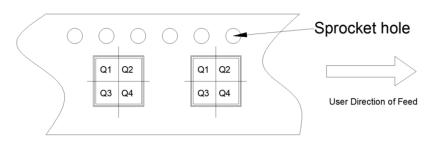

#### **QUADRANT ASSIGNMENTS PIN 1 ORIENTATION TAPE**

#### TAPE DIMENSIONS

| Device       | Package    | Pins | SPQ  | Reel Diameter<br>(mm) | Reel<br>Width W1 | A0   | В0   | K0   | Ρ | w | Pin1 |

|--------------|------------|------|------|-----------------------|------------------|------|------|------|---|---|------|

| GLF4003-D3G7 | DFN 2x3-8L | 8    | 3000 | 180                   | 9                | 3.25 | 2.25 | 0.95 | 4 | 8 | Q1   |

#### Remark:

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- C0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P: Pitch between successive cavity centers

Ultra-low Iq, Asymmetrical Power Mux IC with Priority, Auto & Manual Input Selection

#### **SPECIFICATION DEFINITIONS**

| Document<br>Type             | Meaning                                                                                                                                                                                                                                                                                                                                                                                      | Product Status          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Target<br>Specification      | This is a target specification intended to support exploration and discussion of critical needs for a proposed or target device. Parameters including the typical, minimum, and maximum values are desired, or target. GLF reserves the right to change contents at any time without warning or notification. A target specification will not guarantee the future production of the device. | Design /<br>Development |

| Preliminary<br>Specification | This is a draft version of a product specification which is under internal review and subject to change. GLF reserves the right to change the specification at any time without warning or notification. A preliminary specification will not guarantee the future production of the device.                                                                                                 | Qualification           |

| Product<br>Specification     | This document represents the characteristics of the device.                                                                                                                                                                                                                                                                                                                                  | Production              |

#### DISCLAIMERS

Information in this document is believed to be accurate and reliable, however GLF assumes no liability for errors or omissions. Device performance may be impacted by testing methods and application use cases. Users are responsible to independently evaluate the applicability, usability, and suitability of GLF devices in their application. In no case will GLF be liable for incidental, indirect, or consequential damages associated with the use, misuse, or sale of its product. Customers are wholly responsible to assure GLF devices meet their system level and end product requirements. GLF retains the right to change the information provided in this data sheet without notice.